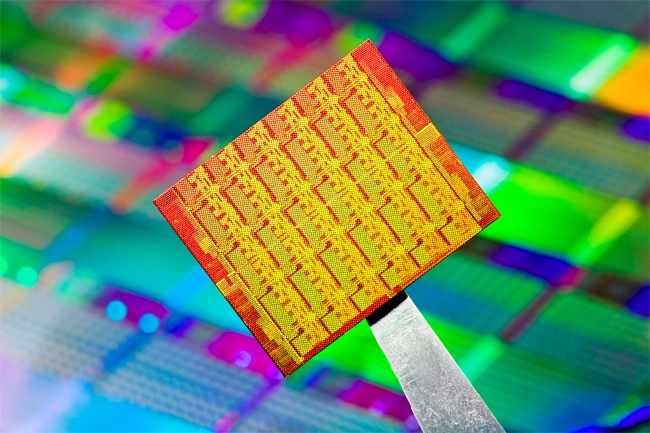

TRAINING WORKSHOPS

Our team is well-prepared to enhance your technical team’s capabilities through thorough training sessions in these key areas.

Technical Training for High Performance Teams

With a collective solid background of 50+ tape-outs at the industry level, our people can help you bridge the gaps in your technical team, with comprehensive training workshops in the following areas

Basic System Verilog

Essential Training for Hardware Description Languages and SystemVerilog:

- Language levels: behavioral, RTL, gate-level

- Basic testbenching and simulation

- Syntax and semantics

- Procedural statements and operators

- User-Defined types and packages

- Interfaces in SystemVerilog

- RTL models for synthesizable combinational and sequential logic

- Basic FSM design

- Simple standard IO: SPI, UART

Advanced System Verilog RTL design for synthesis

Advances in RTL Design with SystemVerilog for Synthesis:

- Best coding practices for synthesizable code in ASICs and FPGAs

- Advanced testbench writing

- Basic RTL design blocks: FIFOs, Arbiters, advanced FSMs, pipelined arithmetic blocks, DSP blocks

- Timing and power convergence: SDF models, back annotation

- Modeling RAM

- Clock domain crossing: synchronizers, testing CDCs

- High speed IO fundamentals

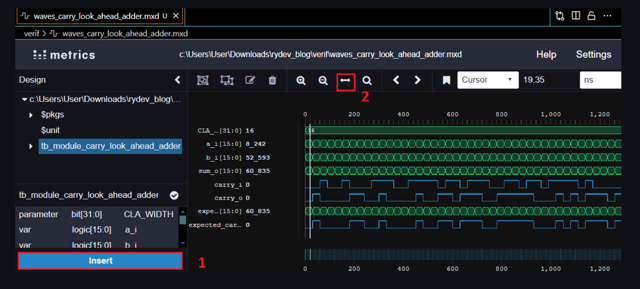

SystemVerilog for Verification

Verification with SystemVerilog: Fundamentals and Advanced Methods:

- Object-Oriented Verification: inheritance and polymorphism

- Testbench modeling constructs, clocking domains: mailboxes, semaphores, specifying randomization constraints, functional coverage and dynamic arrays

- Object Oriented testbenches

- Constrained random verification and coverage

- Overview of SystemVerilog assertions

- Overview of the SystemVerilog Universal Verification Methodology (UVM).

Advanced UVM functional verification

Advanced Functional Verification with UVM Techniques and Applications:

- Transaction level verification.

- Layer verification with UVM.

- Constrained random test generation, coverage, and scoreboarding.

- UVM testbench blocks: phases, class libraries, factories, sequencers, drivers, Monitors, scoreboards.

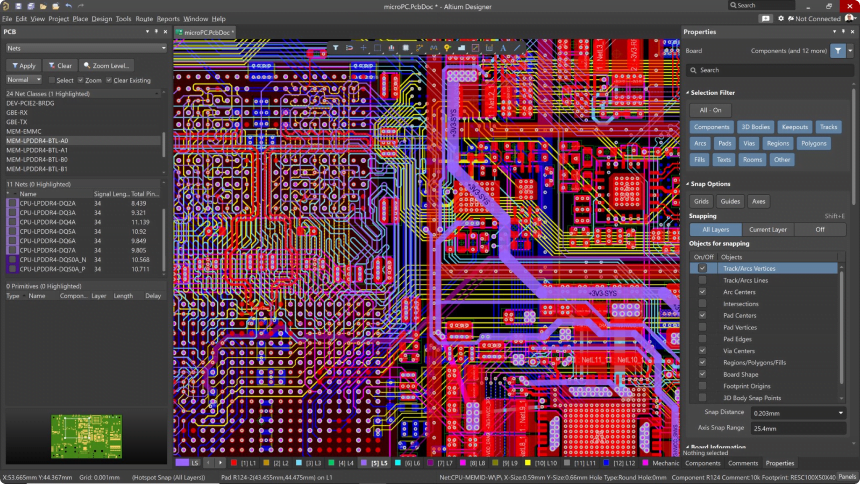

Practical Workshops in EDA

Solutions Adapted to Your Needs

Our hands-on workshops can be delivered onsite in the major EDA tools, or using open flows if necessary at our site.

Please contact us for more information